[컴퓨터구조] 15. Memory

2023.10.10- -

Topics

- Introduction

- Memory System Performance Analysis

- Caches

- Virtual Memory

I/O는 다른 포스팅에서 다루었다.(중요하기 때문에)

- Memory-Mapped I/O

- Summary

Introduction

- Computer performance는 다음에 의존한다.

- Processor performance

- Memory system performance

- RAM

앞서 clock time을 줄이기 위해 노력을 했는데 결국 memory가 안 좋으면 말짱 도루묵이다.

- CPU와 Memory 사이에는 speed gap차이가 상당히 크다.

- CPU: 0.25ns / Mem: 20ns

Processor - Memory Gap

이전 포스팅에서 access memory를 1 clock cycle로 가정했지만, 1980년대 이후에는 그렇지 않았다.

- 점점 processor와 memory의 speed gap이 커지고 있는 모습.

Memory System Challenge

- memory system을 process처럼 빠르게 표시하는 것

- 계층적 memories를 사용하는 것

- 이상적인 memory:

- Fast

- Cheap (inexpensive)

- Large (capacity)

하지만 오직 두 개만 고를 수 있다!

Memory Hierarchy

- 실질적인 data는 main memory에 있다고 생각할 수 있지만 사실은 hard disk에 있고 이를 그 중에서 몇 개만 main memory에 탑재 시켜 놓은 것이다.

- CPU 안에도 Register File이라는 별도의 memory가 존재한다.

- 그래서 사실상 memory hierarchy 맨 꼭대기에는 reg file인 것이다.

- cache에서 register file로 옮겨주는 것은 우리가 앞에서부터 계속 해왔던 것임 -> assembly

- programmer가 작성한 코드에 의해 compiler가 이것을 해줌

- hard disk에서 main memory로 가져오는 것(VM)은 OS가 해준다.

- main memory에서 cache로 가져오는 것은 hardware 적으로 되는 것이다.

- ALU에 들어갈 수 있는 data의 수는 register file이 끽해봐야 32개이기 때문에 32개 미만의 변수만 담을 수 있다.

- 그렇다면 hard disk에서 reg file까지 메모리가 어떻게 전달될까?

- 필요한 것만 가져와서 용량을 맞춘다. (by locality)

Locality

locality를 활용하여 메모리 액세스 속도 향상

한 번 access한 것에 대해 그 근처에 있는 것들을 주로 자주 access 하더라는 경험에 기반한 기법

- Temporal Locality:

- Locality in time

- 최근에 사용했던 거는 머지않아 또 사용될 가능성이 높다.

- How to exploit: 최근 액세스한 데이터를 더 높은 수준의 메모리 계층에 유지

- Spatial Locality:

- Locality in space

- data가 최근에 사용됐으면 그 근처에 있는 데이터가 사용될 가능성이 높다.

- How to exploit: 데이터에 액세스할 때, 근처의 데이터도 더 높은 수준의 메모리 계층으로 가져옵니다

goto를 최대한 사용을 지양하는 이유가 이것이다.(근처에 있는 data를 건너 뛰기 때문에)

Memory Performance

- Hit: 해당 수준의 메모리 계층에서 발견된 데이터

- Miss: 데이터를 찾을 수 없음(다음 레벨로 이동해야 함)

- 만약 data가 miss이면 clock penalty를 감수하고서라도 다음 level에서 가져와야 함.(매우 손해)

= 1 – Hit Rate= 1 – Miss Rate- Average memory access time (AMAT): average time for processor to access data

AMAT = tcache + MRcache[tMM + MRMM(tVM)] - Cache hit일 경우 memory access가 불필요하므로 hit time(tcache)이 AMAT

- Cache miss일 경우 memory acess가 필요하므로 miss에 대한 계산(Miss rate)

- 이대로 이어져서 cache miss이면 main memory에 대해서 진행하고

- 또 main memory miss이면 VM에 대해서 진행한다.

- VM는 반드시 hit일 것이기 때문에 tVM만 곱해짐

- 이대로 이어져서 cache miss이면 main memory에 대해서 진행하고

Cache에 data가 없으면 (miss) main memory에서 가져오는데 10 클락 정도가 소모 되기 때문에 이는 가져올 수 있지만

main memory에 없으면(miss) hard disk에서 가져오는 데는 백만 클락이 소모 되기 때문에 이를 가져오기는 힘들 것이다.

그래서 OS가 그것은 잠깐 fold하고 그와 동시에 다른 task를 수행하도록 하는 technology가 있음.

Memory Performance Example 1

- A program은 2,000 loads and stores를 갖는다.

- 이러한 데이터 값 중 1250은 캐시에 존재한다.

- 메모리 계층의 다른 수준에 의해 공급되는 나머지

- What are the hit and miss rates for the cache?

- Miss Rate = 750/2000 = 0.375 = 1 – Hit Rate

- Hit Rate = 1250/2000 = 0.625

Memory Performance Example 2

- processor가 2 level 계층을 갖는다고 가정: 캐시와 메인메모리

- tcache = 1 cycle, tMM = 100 cycles

- What is the AMAT of the program from Example 1?

- AMAT = tcache + MRcache(tMM) = [1 + 0.375(100)] cycles = 38.5 cycles

Amdahl's Law

- parallelize 가능한 부분 (1-s)

- parallelize 불가능한 부분 (s)

n: parallel processing이 가능한 processor의 수(parallelizable)

s: natured code의 fraction (cannot be parallelized)

- speed-up에 대한 수식을 그래프로 나타내 봤더니 parallel이 불가능한 부분 즉, S term이 커질 수록 speedup이 굉장히 줄어들기 때문에 S term이 중요하다고 볼 수 있다.(bottle neck)

- 즉, S가 무엇이냐에 따라(I/O냐 main memory냐...) 달라지는 것이다.

Memory

- ROM(read만)

- RWM:(read and write; RAM)

- Sequential access (stack이나 queue의 경우 특정 데이터를 가져오려면 pop이나 dequeue가 되어야 함.)

- Random access(RAM): 아무 때나 원할 때 access(by index)

- Read-Only Memory (ROM):

- non-volatile storage(비휘발성, 데이터가 사라지지 않음)

- ROM, PROM, EPROM, EEPROM

- PROM은 field에서 내가 원하는 값을 쓸 수 있도록

- EPROM은 PROM인데 만약 데이터를 틀리게 쓴 경우 버려야 하기 때문에 이때, 지우고 다시 쓸 수 있음(물론 지우는 시간이 많이 걸리긴 하지만)

- EEPROM(Electrical)

- Random Access Memory (RAM):

- Volatile storage

- Static RAM (SRAM)

- 파워가 꺼지면 데이터가 사라짐

- 파워만 있으면 data는 계속 유지된다는 뜻

- Dynamic RAM (DRAM)

- 파워가 연결되어 있더라도 data가 없어지기도 한다.

- 그렇기 때문에 사라지기 전에 read/write하는 refresh 과정이 필요함

- Non-volatile RWM (Flash):

- NAND type: for data

- OR type: for code

SRAM(Static RAM)

- 외부 refresh 없이 데이터를 유지

- Simplicity: 외부 refresh 회로를 요구하지 않음

- Speed: SRAM은 DRAM보다 빠르다.

- Cost: 때때로 DRAM보다 더 비싸다.

- Size: DRAM보다 더 많은 공간을 차지한다.

- SRAM은 6개의 TR가 필요하기 때문에(DRAM은 1개)

- Power: DRAM보다 더 많은 파워를 소모한다.

- Usage: level 1 and level 2 cache

- on-chip memory에 주로 사용됨

SRAM example

- Samsung 1M(eg) x 4 High-speed CMOS SRAM

- 1Meg -> 20-bit address

- Fast access time: 8, 10 ns

- Low power dissipation: 5 mA(standby), 65-80 mA(operating)

https://www.slideserve.com/amity-riley/memory

SRAM (Static RAM)

- 6개의 TR(트랜지스터)

- inverter loop로 인해 데이터가 없어지지 않는다.

- OE: Out enable(read enable)

- OE_L이 low일 때 address값을 읽는데 address가 주어진 그 순간부터 그에 해당하는 data가 읽어지는데 그 때까지 걸린 시간을 read access time이라고 한다.(A to D)

- 즉, address에 해당하는 data가 읽어질 때까지의 시간 -> read access time

DRAM (Dynamic RAM)

- 주기적으로 데이터를 읽어 주어야 함.

- Simple 1-Transistor cell

- 직접적인 power source는 주기적인 refresh를 요구하지 않는다.

- 큰 용량 때문에 address line을 공유한다.

- Two new signals: RAS and CAS

- Row Address Strobe

- Column Address Strobe

- DRAM은 집적도가 높기 때문에 addressing bit에 34bit가 필요한데 이를 17bit의 Row address와 17bit의 Column address를 나누었다.

- 그래서 RAS와 CAS를 통해 memory addressing을 할 수 있는 것이다.

메모리는 정보를 저장(write)하거나 저장된 정보를 읽기(read) 위하여 바둑판과 같이 열(raw, 가로 줄)과 행(column, 세로 줄)으로 구성된 matrix(행렬) 구조의 주소(address)를 가지고 있다.

이를 두고 CAS와 RAS라 부르는데 프로세서가 메모리에 있는 정보를 읽거나 메모리에 정보를 기록할 때는 먼저 가로줄에 신호(RAS, Row Address Strobe)를 보내고 나서 세로줄에 신호(CAS, Column Address Strobe)를 보내어 주소를 확인한다. 어떤 주소에 자료가 들어 있는지 아니면 비어 있는 지는 CAS가 담당하며 CAS 신호가 없어지면 그 주소에 다시 새로운 정보를 저장한다.(따라서 RAS 신호가 앞선다.)

DRAM example

- Samsung 1Mx16 FPM DRAM

- Power: 3.3-5 V, 450-500 mW

- Access time: 50-60 ns

- 10 bit의 address

- 두 개(RAS, CAS) 합쳐서 20bit addressing수행

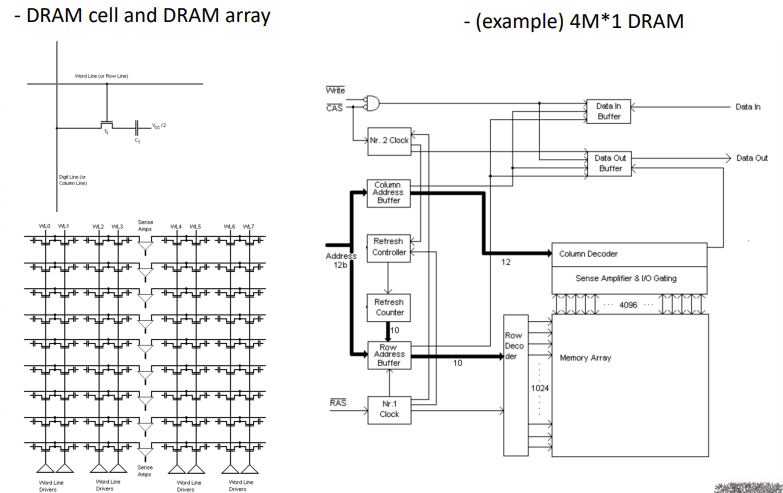

DRAM (Dynamic RAM)

- DRAM cell and DRAM array

- TR 1개

- 0이나 1로 signal을 키워줌

- (example) 4M*1 DRAM

- 사라지기 전에 주기적으로 data를 read/write하는 (refresh)

- capacitor에 charge가 되어있으면 1, 안 되어있으면 0

- RAS, CAS 각각 12 bit -> addressing 24 bit

http://www.cse.scu.edu/~tschwarz/coen180/LN/DRAM.html

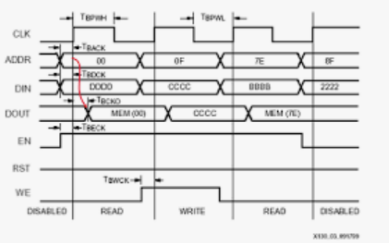

- read/write/burst timing/SDRAM burst read timing

- 1번 그림: read access time

- RAS_L이 먼저 Low가 되었기 때문에 RAS가 먼저 왔고 CAS가 그 다음 왔음을 알 수 있음

- RAS가 오면서 Row address를 읽고

- CAS가 온 순간부터 데이터가 다 읽어질 때까지 걸린 시간을 read access time이라고 함.

- 2번 그림: burst timing

- 연속적인(인접한) 데이터를 계속 가져오기 위해서는(spatial locality) RAS는 계속 두고 CAS의 신호만 계속 바꾸게 하고(바둑판 배열의 메모리에 write하는 과정을 생각해 보면 됨)

- CAS에서만 계속 access

- 그래서 DRAM에서도 연속적인 memory를 access 할 때 굉장히 빠르다 -> burst mode를 사용하기 때문- 3번 그림: write access time

- CAS가 되면서부터 데이터를 쓰기(WE_L)까지 걸린 시간 -> write access time

- 4번 그림: Synchronous DRAM(SDRAM)

Q) 일반적으로 RAS가 먼저 도착하는가?

A) 맞음

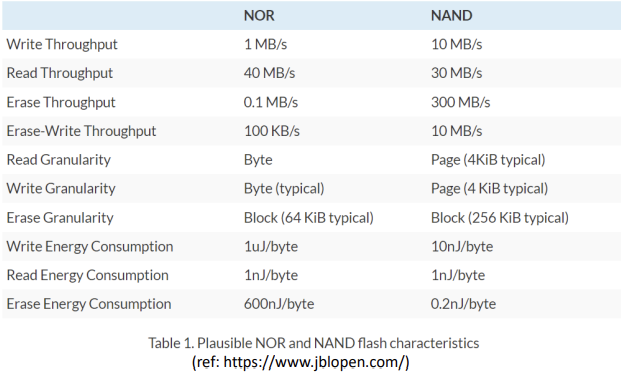

Flash Types

- NOR flash: bit cell like a NOR gate

- Random read/write access

- 임베디드 시스템에서 instruction memory로 사용된다.

- NAND flash: bit cell like a NAND gate

- Denser (bits/area), but block-at-a-time access

- Cheaper per GB

- Used for USB keys, media storage, …

- Flash bits wears out after ~100,000 accesses

- direct RAM이나 disk replacement에 적합하지 않다.

- Wear leveling: 덜 사용되는 block으로 데이터를 remap

- 고루고루 퍼져서 access 할 수 있도록 (FTL)

- 다양한 성능 metric에 대한 비교

- NAND: fast writing

- NOR: byte access

'CS 지식 > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] 16-2. Cache Design (1) | 2023.10.10 |

|---|---|

| [컴퓨터구조] 16-1. Cache (1) | 2023.10.10 |

| [컴퓨터구조] 14-3. Pipelined MIPS Performance and Exception handler (1) | 2023.10.10 |

| [컴퓨터구조] 14-2. Pipelined MIPS - hazard (1) | 2023.10.10 |

| [컴퓨터구조] 14-1. Pipelined MIPS (1) | 2023.10.10 |

소중한 공감 감사합니다